Vivado_DDS IP核_设计与仿真_dds vivado-程序员宅基地

技术标签: IP核 DDS FPGA Vivado Verilog Xilinx

本文介绍Vivado中DDS IP核的使用方法。

文章目录

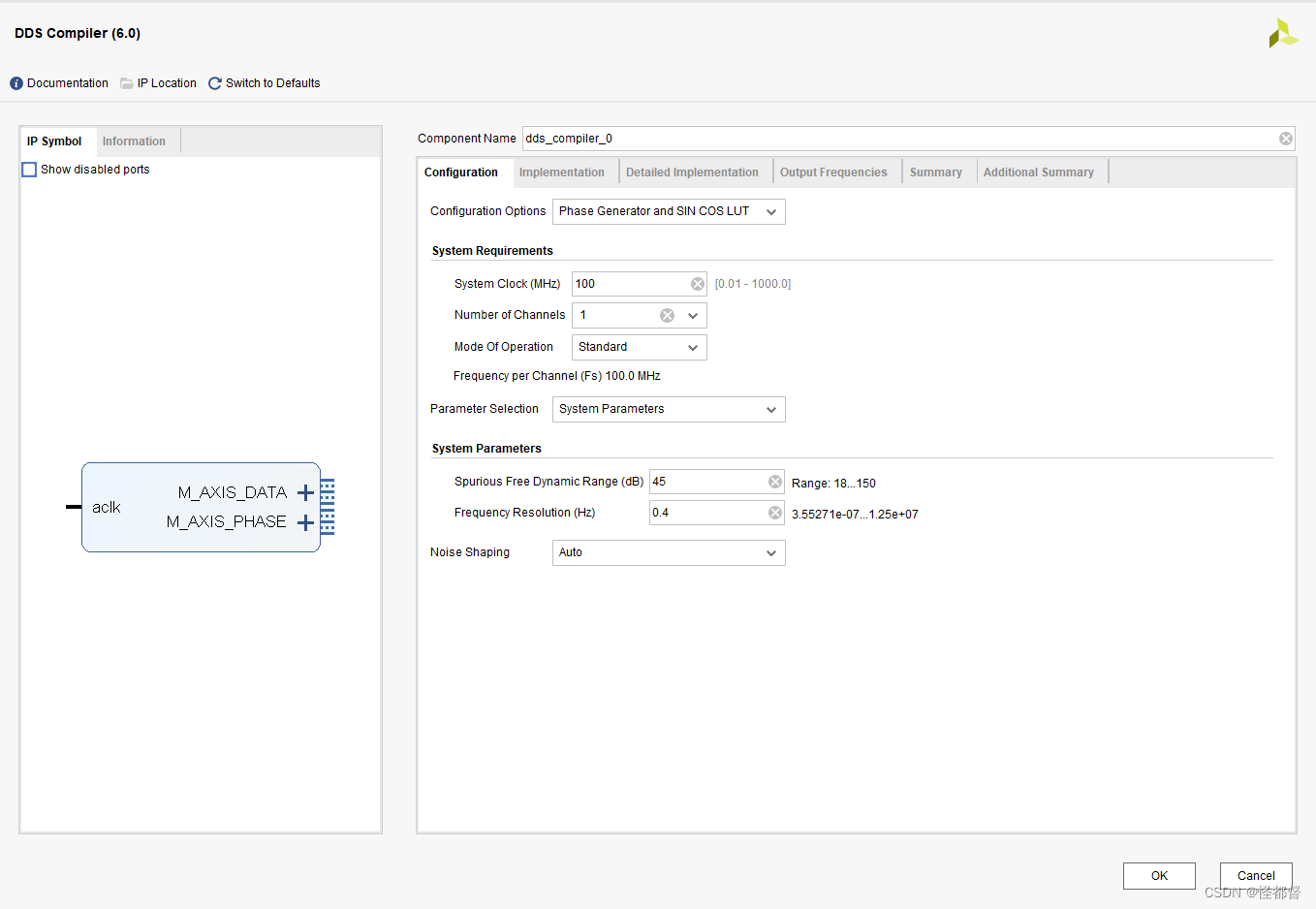

DDS Compiler

首先在IP Catalog中搜索并找到DDS Compiler,双击打开。

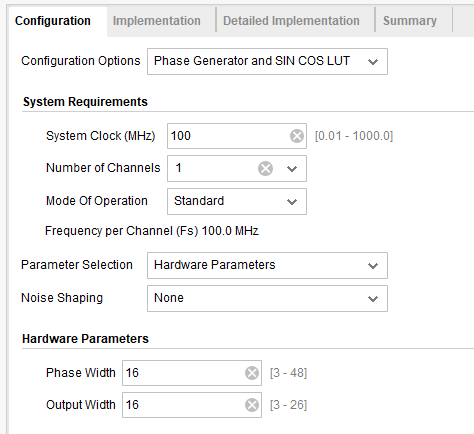

Configuration:

Configuration Options:

Phase Generator and SIN/COS LUT:相位发生器和SIN/COS LUT结合。

Phase Generator only:仅提供相位发生器。

SIN/COS LUT only:仅提供带有可选泰勒级数校正电路的SIN/COS LUT。

注:Phase Generator and SIN/COS LUT 和 SIN/COS LUT only模式的区别在于,前者输入数据代表相位增量,即输入数据保持不变,内核会自动累加相位,后者输入数据代表相位值,即为了得到正确的输出,需要手动更新输入数据。

System Requirements:

System Clock:DDS内核的时钟频率。

Number of Channels:通道数,其会影响每个通道的有效时钟频率,即System Clock除以通道数。

Mode of Operation:DDS操作模式,有standard和rasterized 两种模式可选。

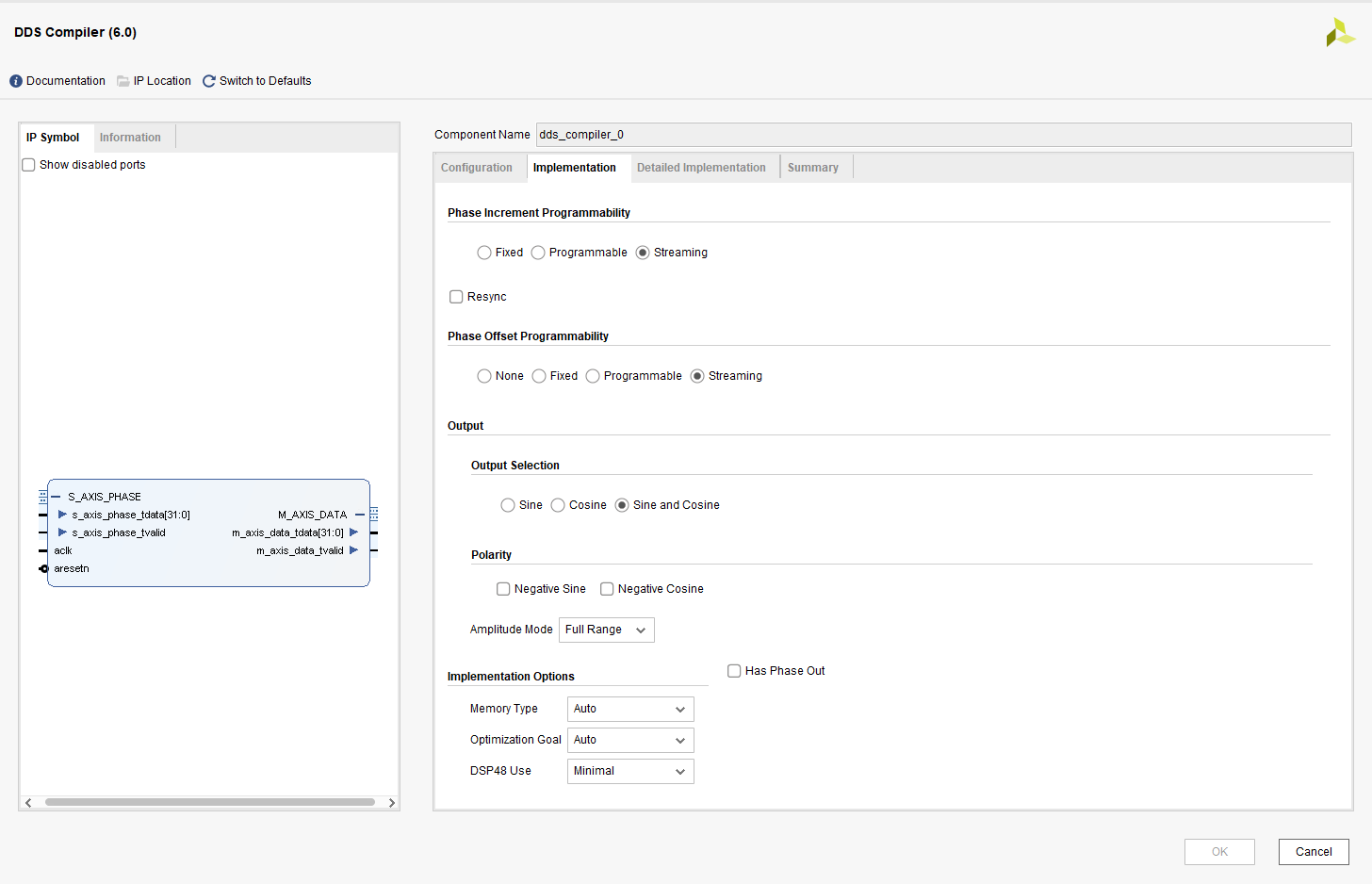

两种模式输出时钟频率计算公式分别为:

Parameter Selection:

System Parameters:

Spurious Free Dynamic Range (dB):无杂散动态范围。

Frequency Resolution (Hz):频率分辨率。

Noise Shaping:噪声成形。

Hardware Parameters:

Phase Width:相位宽度,设置m_axis_phase_tdata中PHASE_OUT字段的宽度。

Output Width:输出宽度,设置m_axis_data_tdata中SINE和COSINE字段的宽度。

对于指定的噪声成形方法,无杂散动态范围和输出宽度存在一定的换算关系。

| Noise Shaping | SFDR |

|---|---|

| None,Dither | SFDR = Output Width x 6 |

| Taylor | SFDR = (Output Width - 1)x 6 |

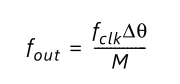

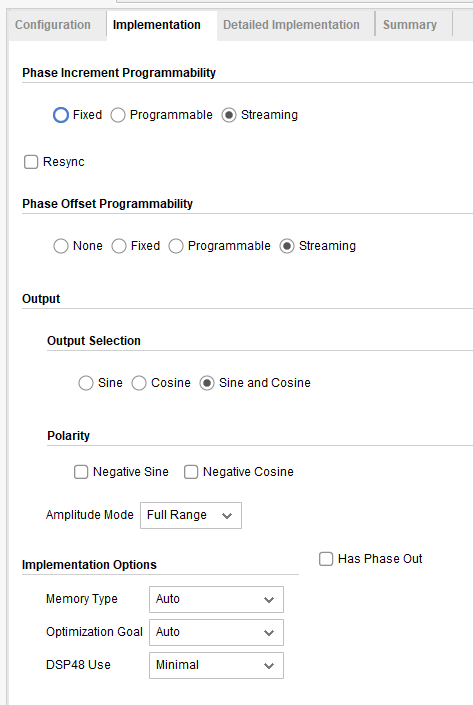

Implementation

Phase Increment Programmability:选择设置 PINC 值的方式。

Phase Offset Programmability:选择设置 POFF 值的方法。

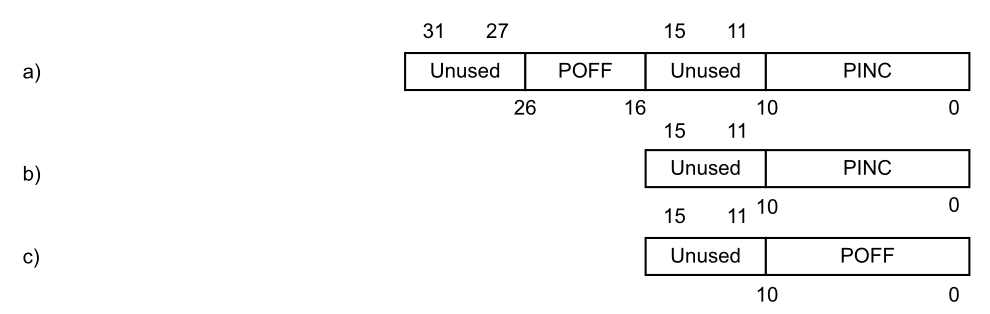

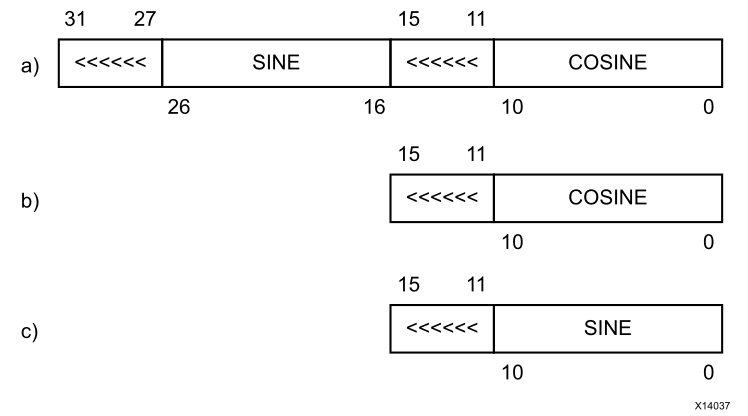

相位增量和相位偏移,在勾选Streaming后,若PINC和POFF分别为11比特,其在s_axis_phase_tdata的位置如下图所示。

Output:

Output Selection:分别勾选Sine and Cosine、Cosine、Sine后,其输出m_axis_data_tdata结构如下图所示。

Ploarity:设置是否翻转m_axis_data_tdata的SINE和COSINE字段。

Amplitude Mode: Full Range和Unit Circle。

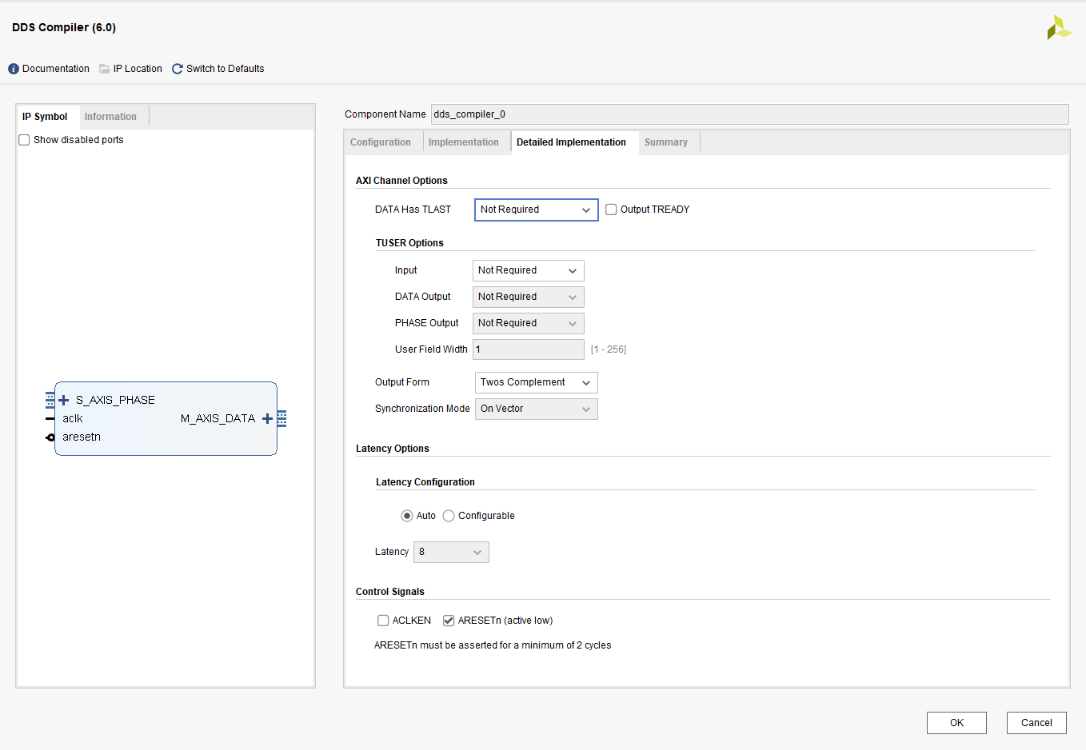

Detailed Implementation:

设置AXI4-Stream接口的相关控制引脚。

仿真

仿真参数设置

仿真代码

`timescale 1ns / 1ps

module DDS_IP_sim;

//input

reg aclk;

reg aresetn;

reg s_axis_phase_tvalid;

reg [31:0] s_axis_phase_tdata;

//output

wire m_axis_data_tvalid;

wire [31:0] m_axis_data_tdata;

wire [15:0] sin;

wire [15:0] cos;

initial begin

aclk = 1'd0;

s_axis_phase_tvalid = 1'd1;

aresetn = 1'd1;

s_axis_phase_tdata[31:16] = 16'h00_00;

s_axis_phase_tdata[15:0] = 16'h0F_FF;

# 5;

forever begin

# 5;

aclk = ~aclk;

end

end

assign sin = m_axis_data_tdata[31:16];

assign cos = m_axis_data_tdata[15:0];

dds_compiler_0 u_dds(

.aclk(aclk), // input wire aclk

.aresetn(aresetn), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(s_axis_phase_tdata), // input wire [31 : 0] s_axis_phase_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata) // output wire [31 : 0] m_axis_data_tdata

);

endmodule

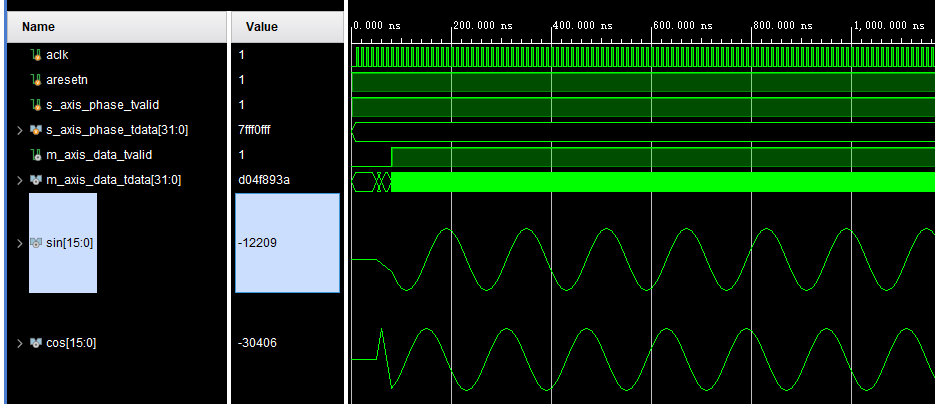

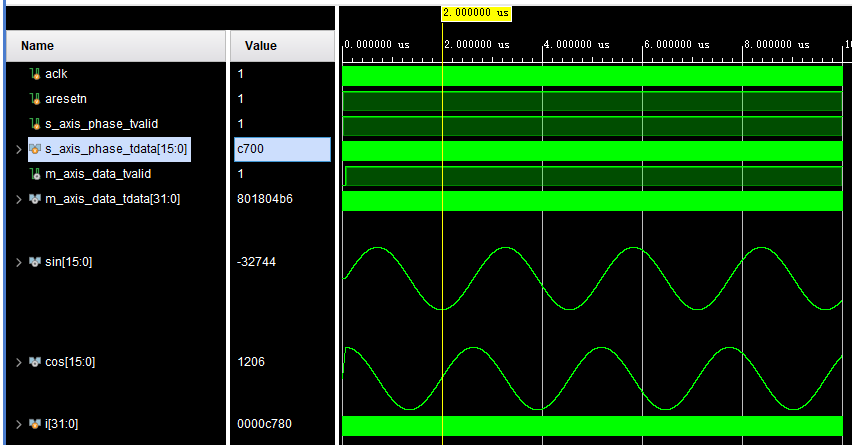

仿真波形

为了便于观察仿真结果,先右击信号,再点击Waveform Style->Analog,再点击Radix->Signed Decimal。

进一步可点击Waveform Style中的Analog Settings,将Interpolation style设置为Hold。

解释一下结果:

时钟频率为100MHz,时钟周期为10ns。phase increment 相位增量为0x0FFF,phase offse相位偏移为0x7FFF,phase width=16。则输出信号相位会落后0x7FFF / 0xFFFF x 360 = 180。输出信号周期为160ns,则输出频率为6.25MHz,满足 输出频率 = 0x0FFF / 0xFFFF x 输入频率。同时可以看到,输出信号sin和cos存在40ns的时差,则对应相差90度。

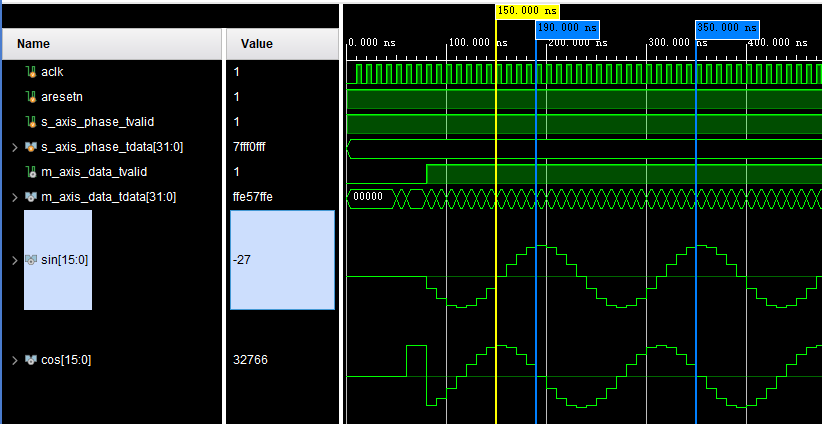

将phase offset相位偏移设置为0x0000,则仿真结果为

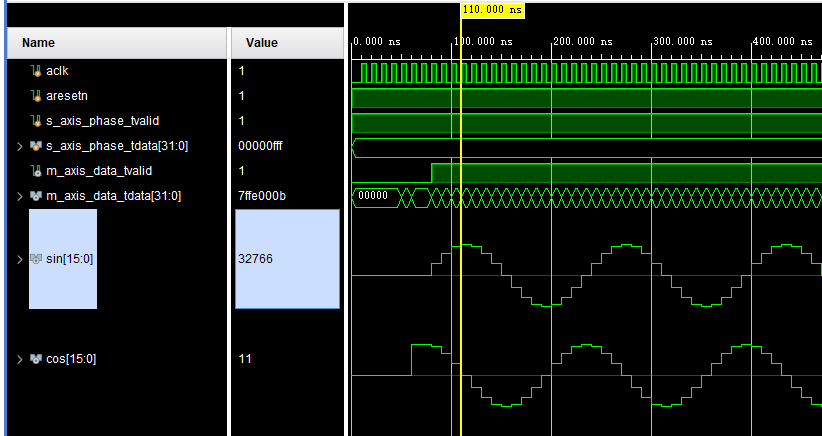

在SIN/COS LUT only操作模式下,需要手动更新s_axis_phase_tdata的值,从下图可以看出该值一直在变化。不同于上图中s_axis_phase_tdata一直保持为0x00000FFF。

智能推荐

什么是内部类?成员内部类、静态内部类、局部内部类和匿名内部类的区别及作用?_成员内部类和局部内部类的区别-程序员宅基地

文章浏览阅读3.4k次,点赞8次,收藏42次。一、什么是内部类?or 内部类的概念内部类是定义在另一个类中的类;下面类TestB是类TestA的内部类。即内部类对象引用了实例化该内部对象的外围类对象。public class TestA{ class TestB {}}二、 为什么需要内部类?or 内部类有什么作用?1、 内部类方法可以访问该类定义所在的作用域中的数据,包括私有数据。2、内部类可以对同一个包中的其他类隐藏起来。3、 当想要定义一个回调函数且不想编写大量代码时,使用匿名内部类比较便捷。三、 内部类的分类成员内部_成员内部类和局部内部类的区别

分布式系统_分布式系统运维工具-程序员宅基地

文章浏览阅读118次。分布式系统要求拆分分布式思想的实质搭配要求分布式系统要求按照某些特定的规则将项目进行拆分。如果将一个项目的所有模板功能都写到一起,当某个模块出现问题时将直接导致整个服务器出现问题。拆分按照业务拆分为不同的服务器,有效的降低系统架构的耦合性在业务拆分的基础上可按照代码层级进行拆分(view、controller、service、pojo)分布式思想的实质分布式思想的实质是为了系统的..._分布式系统运维工具

用Exce分析l数据极简入门_exce l趋势分析数据量-程序员宅基地

文章浏览阅读174次。1.数据源准备2.数据处理step1:数据表处理应用函数:①VLOOKUP函数; ② CONCATENATE函数终表:step2:数据透视表统计分析(1) 透视表汇总不同渠道用户数, 金额(2)透视表汇总不同日期购买用户数,金额(3)透视表汇总不同用户购买订单数,金额step3:讲第二步结果可视化, 比如, 柱形图(1)不同渠道用户数, 金额(2)不同日期..._exce l趋势分析数据量

宁盾堡垒机双因素认证方案_horizon宁盾双因素配置-程序员宅基地

文章浏览阅读3.3k次。堡垒机可以为企业实现服务器、网络设备、数据库、安全设备等的集中管控和安全可靠运行,帮助IT运维人员提高工作效率。通俗来说,就是用来控制哪些人可以登录哪些资产(事先防范和事中控制),以及录像记录登录资产后做了什么事情(事后溯源)。由于堡垒机内部保存着企业所有的设备资产和权限关系,是企业内部信息安全的重要一环。但目前出现的以下问题产生了很大安全隐患:密码设置过于简单,容易被暴力破解;为方便记忆,设置统一的密码,一旦单点被破,极易引发全面危机。在单一的静态密码验证机制下,登录密码是堡垒机安全的唯一_horizon宁盾双因素配置

谷歌浏览器安装(Win、Linux、离线安装)_chrome linux debian离线安装依赖-程序员宅基地

文章浏览阅读7.7k次,点赞4次,收藏16次。Chrome作为一款挺不错的浏览器,其有着诸多的优良特性,并且支持跨平台。其支持(Windows、Linux、Mac OS X、BSD、Android),在绝大多数情况下,其的安装都很简单,但有时会由于网络原因,无法安装,所以在这里总结下Chrome的安装。Windows下的安装:在线安装:离线安装:Linux下的安装:在线安装:离线安装:..._chrome linux debian离线安装依赖

烤仔TVの尚书房 | 逃离北上广?不如押宝越南“北上广”-程序员宅基地

文章浏览阅读153次。中国发达城市榜单每天都在刷新,但无非是北上广轮流坐庄。北京拥有最顶尖的文化资源,上海是“摩登”的国际化大都市,广州是活力四射的千年商都。GDP和发展潜力是衡量城市的数字指...

随便推点

java spark的使用和配置_使用java调用spark注册进去的程序-程序员宅基地

文章浏览阅读3.3k次。前言spark在java使用比较少,多是scala的用法,我这里介绍一下我在项目中使用的代码配置详细算法的使用请点击我主页列表查看版本jar版本说明spark3.0.1scala2.12这个版本注意和spark版本对应,只是为了引jar包springboot版本2.3.2.RELEASEmaven<!-- spark --> <dependency> <gro_使用java调用spark注册进去的程序

汽车零部件开发工具巨头V公司全套bootloader中UDS协议栈源代码,自己完成底层外设驱动开发后,集成即可使用_uds协议栈 源代码-程序员宅基地

文章浏览阅读4.8k次。汽车零部件开发工具巨头V公司全套bootloader中UDS协议栈源代码,自己完成底层外设驱动开发后,集成即可使用,代码精简高效,大厂出品有量产保证。:139800617636213023darcy169_uds协议栈 源代码

AUTOSAR基础篇之OS(下)_autosar 定义了 5 种多核支持类型-程序员宅基地

文章浏览阅读4.6k次,点赞20次,收藏148次。AUTOSAR基础篇之OS(下)前言首先,请问大家几个小小的问题,你清楚:你知道多核OS在什么场景下使用吗?多核系统OS又是如何协同启动或者关闭的呢?AUTOSAR OS存在哪些功能安全等方面的要求呢?多核OS之间的启动关闭与单核相比又存在哪些异同呢?。。。。。。今天,我们来一起探索并回答这些问题。为了便于大家理解,以下是本文的主题大纲:[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-JCXrdI0k-1636287756923)(https://gite_autosar 定义了 5 种多核支持类型

VS报错无法打开自己写的头文件_vs2013打不开自己定义的头文件-程序员宅基地

文章浏览阅读2.2k次,点赞6次,收藏14次。原因:自己写的头文件没有被加入到方案的包含目录中去,无法被检索到,也就无法打开。将自己写的头文件都放入header files。然后在VS界面上,右键方案名,点击属性。将自己头文件夹的目录添加进去。_vs2013打不开自己定义的头文件

【Redis】Redis基础命令集详解_redis命令-程序员宅基地

文章浏览阅读3.3w次,点赞80次,收藏342次。此时,可以将系统中所有用户的 Session 数据全部保存到 Redis 中,用户在提交新的请求后,系统先从Redis 中查找相应的Session 数据,如果存在,则再进行相关操作,否则跳转到登录页面。此时,可以将系统中所有用户的 Session 数据全部保存到 Redis 中,用户在提交新的请求后,系统先从Redis 中查找相应的Session 数据,如果存在,则再进行相关操作,否则跳转到登录页面。当数据量很大时,count 的数量的指定可能会不起作用,Redis 会自动调整每次的遍历数目。_redis命令

URP渲染管线简介-程序员宅基地

文章浏览阅读449次,点赞3次,收藏3次。URP的设计目标是在保持高性能的同时,提供更多的渲染功能和自定义选项。与普通项目相比,会多出Presets文件夹,里面包含着一些设置,包括本色,声音,法线,贴图等设置。全局只有主光源和附加光源,主光源只支持平行光,附加光源数量有限制,主光源和附加光源在一次Pass中可以一起着色。URP:全局只有主光源和附加光源,主光源只支持平行光,附加光源数量有限制,一次Pass可以计算多个光源。可编程渲染管线:渲染策略是可以供程序员定制的,可以定制的有:光照计算和光源,深度测试,摄像机光照烘焙,后期处理策略等等。_urp渲染管线