FPGA-LCD基础驱动_fpga lcd cnt-程序员宅基地

技术标签: # FPGA学习篇

LCD的接口时序波形如图所示。VSYNC是场同步信号,低电平有效,从时序图可以看出,VSYNC是每一场(即也可以理解为每送一幅完整图像)的同步信号;与此类似,HSYNC是行同步信号,也是在每一行数据传输的开始产生几个时钟周期的低脉冲。这两个信号用于同步当前的数据信号,根据固定的脉冲约定,我们在某些时钟上升沿前将图像数据送到数据总线上供LCD内部锁存。

LCD驱动时序波形

这是LCD时序图中对应的时间参数。

表8.11 LCD驱动时序参数表

| 信号 |

列项 |

标记 |

最小值 |

标准值 |

最大值 |

单位 |

| Dclk |

频率 |

Tosc |

156 |

ns |

||

| 最大时间 |

Tch |

78 |

ns |

|||

| 最小时间 |

Tcl |

78 |

ns |

|||

| Data |

建立时间 |

Tsu |

12 |

ns |

||

| 保持时间 |

Thd |

12 |

ns |

|||

| Hsync |

周期 |

TH |

408 |

Tosc |

||

| 脉冲宽度 |

THS |

5 |

30 |

Tosc |

||

| 后沿 |

THB |

38 |

Tosc |

|||

| 显示周期 |

TEP |

320 |

Tosc |

|||

| 同步周期 |

THE |

36 |

68 |

88 |

Tosc |

|

| 前沿 |

THF |

20 |

Tosc |

|||

| Vsync |

周期 |

TV |

262 |

TH |

||

| 脉冲宽度 |

TVS |

1 |

3 |

5 |

TH |

|

| 后沿 |

TVB |

15 |

TH |

|||

| 显示周期 |

TVD |

240 |

TH |

|||

| 前沿 |

TVF |

2 |

4 |

TH |

相同的方式驱动的程序写法类似:

顶层文件:

module top(ext_clk_25m,ext_rst_n,lcd_light_en,lcd_clk,lcd_hsy,lcd_vsy,lcd_r,lcd_g,lcd_b

);

input ext_clk_25m;

input ext_rst_n;

output lcd_light_en;

output lcd_clk;

output lcd_hsy;

output lcd_vsy;

output [4:0] lcd_r;

output [5:0] lcd_g;

output [4:0] lcd_b;

lcd_controller uut_lcd_controller(

.clk(ext_clk_25m),

.rst_n(ext_rst_n),

.lcd_light_en(lcd_light_en),

.lcd_clk(lcd_clk),

.lcd_hsy(lcd_hsy),

.lcd_vsy(lcd_vsy),

.lcd_r(lcd_r),

.lcd_g(lcd_g),

.lcd_b(lcd_b)

);

endmodule

lcd_controller.v

module lcd_controller(clk,rst_n,lcd_light_en,lcd_clk,lcd_hsy,lcd_vsy,lcd_r,lcd_g,lcd_b

);

input clk;

input rst_n;

output lcd_light_en;

output lcd_clk;

output reg lcd_hsy;

output reg lcd_vsy;

output [4:0] lcd_r;

output [5:0] lcd_g;

output [4:0] lcd_b;

parameter HSY_TH=9'D408-1'D1;//周期

parameter HSY_THS=9'D30 ;//脉冲宽度

parameter HSY_THB=9'D38 ;//后沿

parameter HSY_TEP=9'D320 ;//显示周期

parameter HSY_THE=9'D68 ;//同步周期

parameter HSY_THF=9'D20 ;//前沿

parameter VSY_TV=9'D262-1'D1;//周期

parameter VSY_TVS=9'D3 ;//脉冲宽度

parameter VSY_TVB=9'D15 ;//后沿

parameter VSY_TVD=9'D240 ;//显示周期

parameter VSY_TVF=9'D4 ;//前沿

//lcd背光常开

assign lcd_light_en=1'b1;

//配置驱动时钟6.25mHz

reg [1:0] lcd_cnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_cnt<=1'b0;

end

else begin

lcd_cnt<=lcd_cnt+1'b1;

end

end

assign lcd_clk=lcd_cnt[1];

wire dchange ={lcd_cnt==2'd2};

//X和Y轴计数器

reg[8:0] xcnt;

reg[8:0] ycnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

xcnt<=1'b0;

end

else if(dchange==1'b1)begin

if(xcnt==HSY_TH)begin

xcnt<=1'b0;

end

else begin

xcnt<=xcnt+1'b1;

end

end

else;

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

ycnt<=1'b0;

end

else if(dchange&&xcnt==HSY_TH)begin

if(ycnt==VSY_TV)begin

ycnt<=1'b0;

end

else begin

ycnt<=ycnt+1'b1;

end

end

else begin

ycnt<=ycnt;

end

end

//lcd显示的有效区域

reg valid;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

valid<=1'b0;

end

else if(ycnt>=(VSY_TVS+VSY_TVB)&&ycnt<(VSY_TVS+VSY_TVB+VSY_TVD)&&

xcnt>=(HSY_THS+HSY_THB)&&xcnt<(HSY_TEP+HSY_THB+HSY_THE))begin

valid<=1'b1;

end

else begin

valid<=1'b0;

end

end

//LCD驱动行场同步信号产生逻辑

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_hsy<=1'b1;

end

else if(xcnt==1'b0)begin

lcd_hsy<=1'b0;

end

else if(xcnt>=HSY_THS)begin

lcd_hsy<=1'b1;

end

else begin

lcd_hsy<=lcd_hsy;

end

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_vsy<=1'b1;

end

else if(ycnt==1'b0)begin

lcd_vsy<=1'b0;

end

else if(ycnt>=VSY_TVS)begin

lcd_vsy<=1'b1;

end

else begin

lcd_vsy<=lcd_vsy;

end

end

//产生显示条纹

reg [3:0]tmp_cnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

tmp_cnt<=1'b0;

end

else if(valid==1'b0)begin

tmp_cnt<=1'b0;

end

else if(valid&&dchange)begin

if(tmp_cnt<4'd9)begin

tmp_cnt<=tmp_cnt+1'b1;

end

else begin

tmp_cnt<=1'b0;

end

end

end

reg [15:0]lcd_db_rgb;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_db_rgb<=16'd0;

end

else if(valid)begin

if((tmp_cnt==4'd9)&&dchange)begin

lcd_db_rgb[15:11]<=lcd_db_rgb[15:11]+1'b1;

end

else;

end

else begin

lcd_db_rgb<=1'b0;

end

end

assign lcd_r =valid ? lcd_db_rgb[15:11]:5'd0;

assign lcd_g =valid ? lcd_db_rgb[10:5]:6'd0;

assign lcd_b =valid ? lcd_db_rgb[4:0]:5'd0;

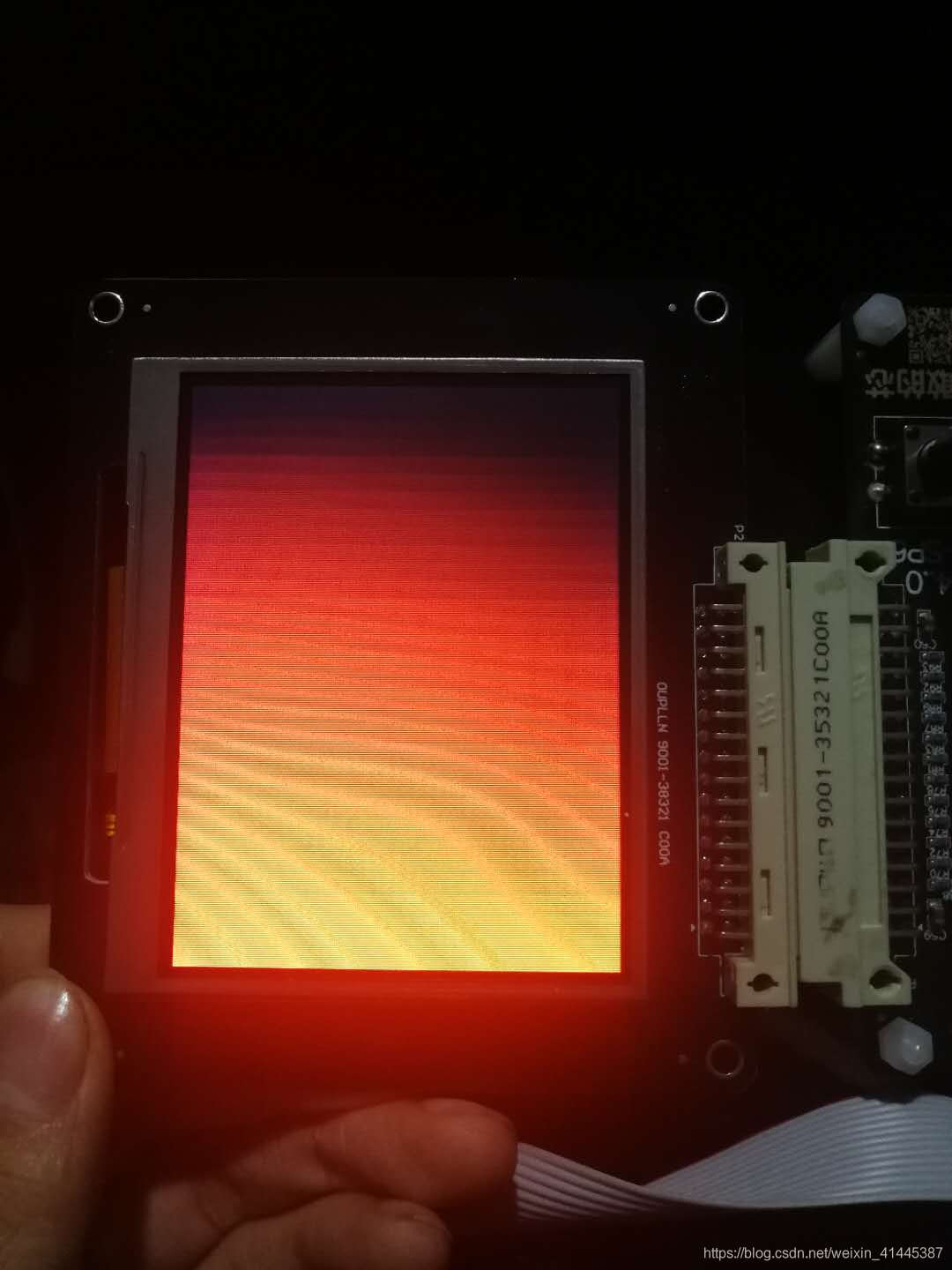

endmodule下板子效果图:

智能推荐

Linux安装JDK1.8 & tomcat & MariaDB(MySQL删减版) & MySQL安装(重要)-程序员宅基地

文章浏览阅读752次,点赞24次,收藏18次。Linux安装JDK1.8 & tomcat & MariaDB(MySQL删减版) & MySQL安装(重要)

神经网络学习小记录20——ResNet50模型的复现详解_resnet50复现-程序员宅基地

文章浏览阅读6.8w次,点赞184次,收藏941次。神经网络学习小记录20——ResNet50模型的复现详解学习前言什么是残差网络什么是ResNet50模型ResNet50网络部分实现代码图片预测学习前言最近看yolo3里面讲到了残差网络,对这个网络结构很感兴趣,于是了解到这个网络结构最初的使用是在ResNet网络里。什么是残差网络Residual net(残差网络):将靠前若干层的某一层数据输出直接跳过多层引入到后面数据层的输入部分。..._resnet50复现

AI之Tool:机器学习/深度学习常用工具(python/Anaconda等)的简介、安装、使用方法之详细攻略_python库 ai robot tool 怎么用起来-程序员宅基地

文章浏览阅读1.7k次,点赞18次,收藏21次。Matlab是一种用于科学计算和工程领域的高级编程语言和环境,广泛用于数学建模、数据分析和信号处理。它有丰富的库和框架,如NumPy、Pandas、Scikit-learn、TensorFlow和PyTorch,使其成为研究和实际应用中的首选语言。:Java在企业级应用中有很大的影响力,而且也有一些用于机器学习和深度学习的库,如Deeplearning4j。: 由GitHub开发,是一个开源的文本编辑器,支持Python和其他多种语言。: Python的标准发行版中自带的简单集成开发环境,适合初学者。_python库 ai robot tool 怎么用起来

N76E003初次搭建工程及遇到Keil 警告:UNCALLED SEGMENT,IGNORED FOR OVERLAY PROCESS时的解决方案_*** warning l25: data types different-程序员宅基地

文章浏览阅读1.7k次。问题描述初次接触N76E003开发板,主要根据以下三篇文章搭建了基本的环境:[N76E003安装环境教程] https://www.cnblogs.com/zhugeanran/p/9554822.html (本文调试遇到警告例子为该文末尾程序)[N76快速入门及常见坑] https://blog.csdn.net/qlexcel/article/details/81069808[单片机..._*** warning l25: data types different

引用和指针的区别-程序员宅基地

文章浏览阅读640次。引用即句柄,都是根据Java编程思想翻译过来的没什么区别。 CSDN有很多大牛,当然也有不少傻逼,并不是所有的程序员都很可爱呆萌,正如并不是所有的牛奶都叫特仑苏。 曾经就有傻逼跟我说java里有指针,数组就实现了,不要相信大学书本里的那套,我就想问问,这么看不起大学,你TM到是上个大学给我看看啊。java为了防止内存泄漏放弃了指针这一概念和用法。指针是什么?java是如何实现指向对象的功能_引用和指针的区别

speex编解码在android上实现-程序员宅基地

文章浏览阅读1.6k次。上一篇文章已经对speex的工作原理做介绍。这里是android端的编译方法。 以前在应用中使用到了Speex编解码,近来总结了一下Speex在android上的实现。Speex是一套主要针对语音的开源免费,无专利保护的音频压缩格式。Speex工程着力于通过提供一个可以替代高性能语音编解码来降低语音应用输入门槛 。另外,相对于其它编解码,Speex也很适合网络应用,在网络应用上有着自己独特的优势。

随便推点

“无用发明家”告诉你,5G推开了三重门-程序员宅基地

文章浏览阅读141次。不知道从什么时候起,“无用发明家”的概念开始兴起。国内有大家耳熟能详的手工耿,日本有“无用发明家”麻里菜。这些动手能力极强的视频博主,不断向观众展示一件件极富创意却并没有什么用处的作品,成...

【MySQL】数据库的安装与连接, 常见问题的解决-程序员宅基地

文章浏览阅读126次。文章目录Mysql 8数据库学习的目的数据库的三种模型层次模型网状模型关系模型Mysql 8 常见问题安装window时遇到的一些问题安装Linux时遇到的一些问题连接数据库在系统终端中工具中Mysql 8数据库学习的目的1.数据可持久化保存2.方便统一化管理以及实现结构化查询本质上数据库是一个按照特定的规则存储在磁盘上的一个用来存储数据的仓库, 通过数据库管理系统,统一的对其中储存的数据进行管理和使用.数据库的三种模型层次模型层次模型就是按照数据类型的层次关系来分类优点: -->查

Spring Cloud系列(一)之 Eureka、Zookeeper、Consul_springcloud和zookeeper学习先后-程序员宅基地

文章浏览阅读1.1k次。Spring Cloud系列之Eureka、Zookeeper、Consul一、微服务架构介绍1.1 架构的演变1.2 Spring Cloud介绍二、微服务架构业务场景2.1 创建服务提供者(provider)工程2.2 创建服务消费者(consumer)工程三、Eureka服务注册与发现3.1 搭建注册中心3.2 服务注册(消费者集群)3.2.1 服务提供者注册3.2.2 服务消费者注册3.3 EurekaServer集群环境构建3.4 搭建服务提供者集群和负载均衡3.5 微服务信息完善3.6 服务发现_springcloud和zookeeper学习先后

计算机网络主要由哪三个部分组成,计算机网络由哪几个部份组成-程序员宅基地

文章浏览阅读3.9k次。大家好,我是时间财富网智能客服时间君,上述问题将由我为大家进行解答。计算机网络由计算机、网络操作系统、传输介质(可以是有形的,也可以是无形的,如无线网络的传输介质就是空气)以及相应的应用软件四部分组成。计算机网络(computer network),简称网络,是利用通信设备和线路将地理位置不同的、功能独立的多个计算机系统连接起来,以功能完善的网络软件实现网络的硬件、软件及资源共享和信息传递的系统,..._计算机网络主要由网络硬件、网络操作系统、网络应用程序三个部分组成,这三个部分

斐波那契数列对10007取余数_斐波拉契数列c++余数10007-程序员宅基地

文章浏览阅读1.1k次,点赞2次,收藏2次。Mn = ( Mn-1 + Mn-2 ) % 10007因为*F(n) = X1 * 10007 + MnF(n+1) = X2 * 10007 +Mn+1F(n+2) = F(n) + F(n+1)=(X1 + X2)+100007 + Mn + Mn+1Mn+2 = F(n+2) / 10007 = Mn + Mn+1所以 Mn = ( Mn-1 + Mn-2 ) % 10007..._斐波拉契数列c++余数10007

SRGAN损失函数(目标函数)详解_srgan的损失函数-程序员宅基地

文章浏览阅读7.9k次,点赞7次,收藏44次。SRGAN损失函数的解析及其Keras代码实现_srgan的损失函数